# The research of some key technologies of compiler optimization for on-chip multi-core processor

# Introduction

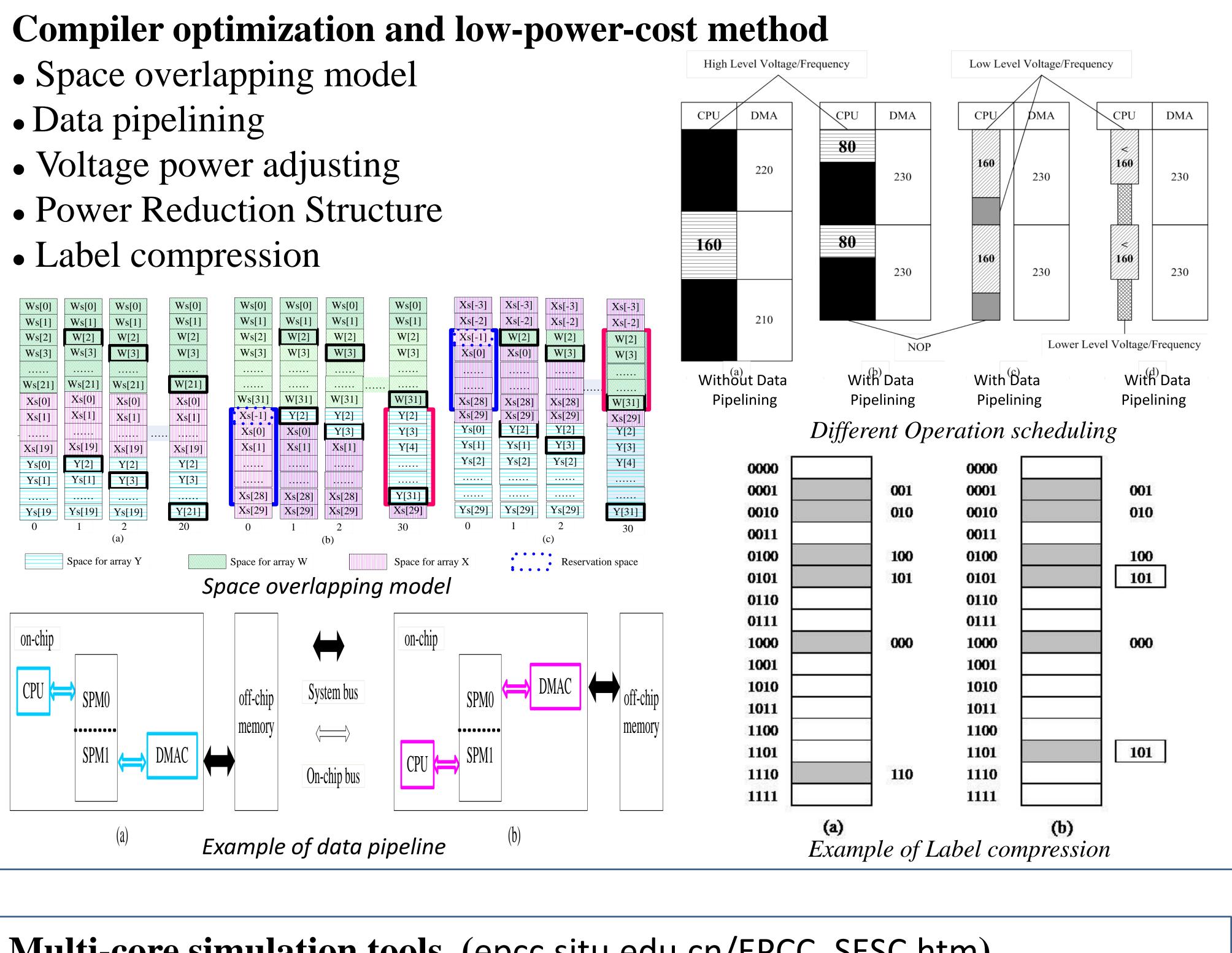

Multi/Many-core processor is the inevitable trend of development of processor, and has been applied in desktop, server and mobile and embedded system. However, the power, memory and the parallelization of software limited the development of multi-core processor. In this project, we studied several key technologies of the optimization for on-chip multi-core compiler processor: Architecture of Multi-core Processor, Acceleration Model, **Compiler Optimization**, Low-power framework and methods, Task Stealing Scheduling etc.

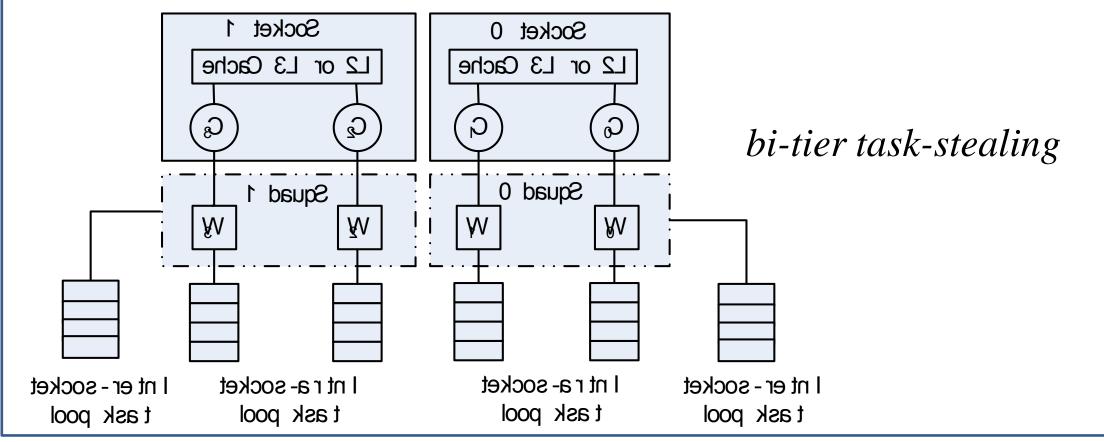

#### **Multi-core Processor Modeling** •Scratch Pad Memory Model

- ©Characteristic: Small-Capacity; low-power Consumption; highspeed access

- O Allocation strategy: Static Allocation; Dynamic allocation

### • Data Pipeline Model

- Operation Dynamic voltage scaling

- Instruction-level speed modeling

- © Graphical data fetch modeling

- ◎ Independence between DMA and CPU

- O Data Predictability from loop iteration

# • Power Cost Model

- Quantify static power consumption

- Quantify command power

A second second

- Quantify power of cache and memory access

- Multi-core communication power modeling

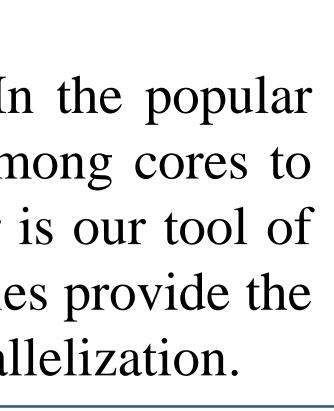

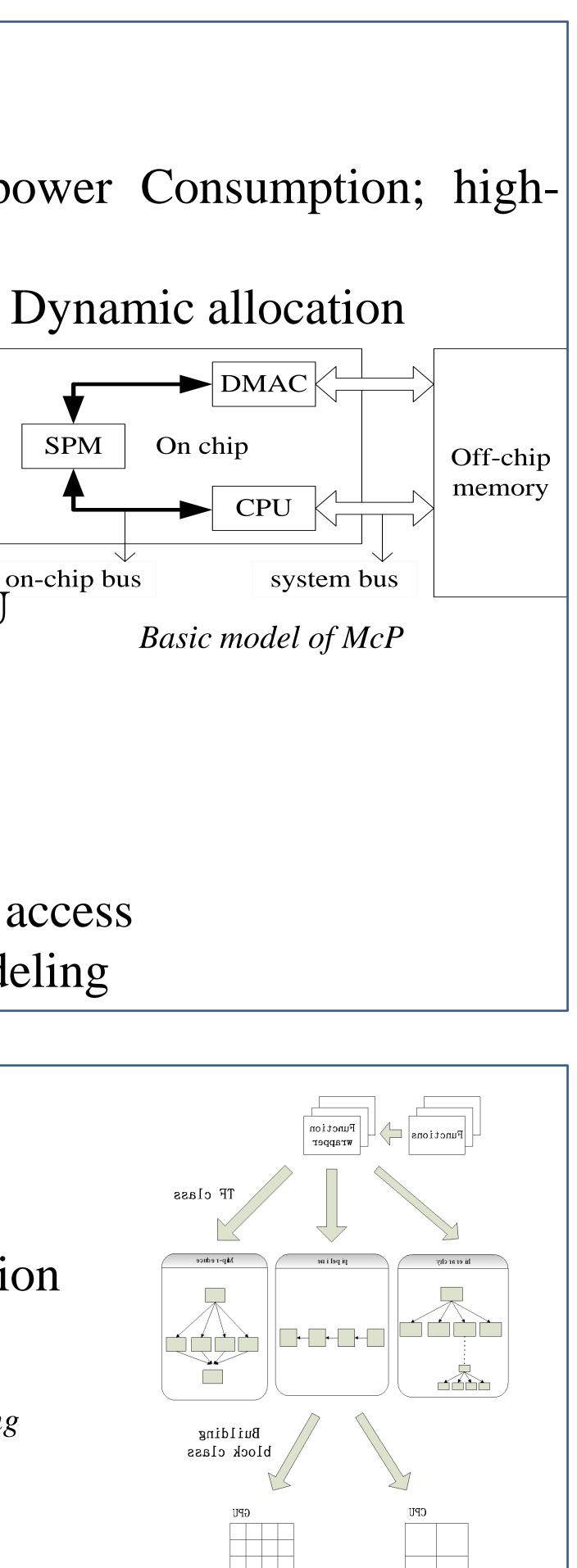

#### **Multi-thread parallelization**

- Template Meta-programming method

- Architecture of bi-tier task-stealing

- Cycle of sentence migration transformation

This material is based upon work supported in part by China National Funds for Distinguished Young Scientists Projects No. 60725208

|  | S | ] |

|--|---|---|

|  |   |   |

|  |   |   |

Programming Model Overview

# Conclusion

We use compiler to analyze and optimize user programs automatically. In the popular multi-core architecture scenario, the optimized programs are scheduled among cores to save power with guarantee of no vital performance degradation. Compiler is our tool of achieving high performance and low power consumption. These technologies provide the support for high-performance computer, cloud computing and software parallelization.

**Minyi Guo** (guo-my@cs.sjtu.edu.cn) Director Professor of Embedded Pervasive Computing Center, Chairman of Department of Computer Science and Engineering, Shanghai Jiao Tong University, China.